Scaling

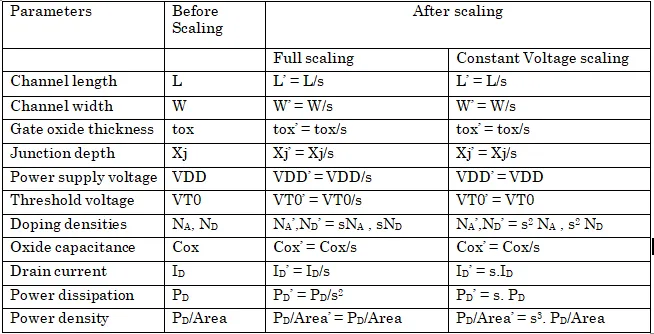

Reducing the channel length of a MOSFET can be described in terms of scaling theory. A scaling parameter S (S < 1) is used to scale the dimensions of a MOSFET. The value of S is typically in the neighborhood of 0.7 from one CMOS technology generation to the next. For example, if a process uses a VDD of 2 V, a next generation process would use a VDD of 1.4 V. In other words VDD'= VDD.S The channel length of the scaled process is reduced to L'=L.S while the width is reduced to W=W.S

· The design of high-density chips in MOS VLSI (Very Large Scale Integration) technology requires that the packing density of MOSFETs used in the circuits is as high as possible and, consequently, that the sizes of the transistors are as small as possible. The reduction of the size, i.e., the dimensions of MOSFETs, is commonly referred to as scaling.

· In order to meet the demand of high density chips in MOS technology, it is required that MOSFET are scaled down i.e. reduction in the size of transistor, so that high packaging density can be achieved.

· Thus scaling of MOSFET transistor is concerned with systematic reduction of overall dimension of the device as allowed by available technology, while preserving the geometric ratios found in the larger devices.

· A constant scaling factor ‘s’ is introduced. The scaled device is obtained by dividing all horizontal and vertical dimensions of the large size transistor by this scaling factor.

· It is expected that the operational characteristics of the MOS transistor will change with the reduction of its dimension.

Advantages of scaling:

![]() Increases the switching speed.

Increases the switching speed.

![]() Reduces chip size.

Reduces chip size.

![]() Reduces power dissipation.

Reduces power dissipation.

Disadvantages of scaling:

o Effect on SiO2 thickness – on scaling oxide thickness eventually a sage will reach when oxide will lose its dielectric property.

o Subthreshold current – For smaller device, in addition to VGS voltage, VDS voltage also has greater influence on the carrier flow in the channel. The carrier in the channel can be increased by increasing VDS voltage & also potential barrier can be reduced even VGS < VT. Thus, resulting current through the channel for higher values of VDS is called sub-threshold current.

o Noise problem – Scaling process inevitably results in noise problem, which degrades the reliability of high density chip.

Types of scaling:

1. Full scaling/ Constant field scaling:

Ø The Full scaling technique attempts to preserve the magnitude of internal electric fields in the MOSFET, while the dimensions are scaled down by factor of ‘s’.

Ø To achieve this goal the potentials must be scaled down proportionally, by the same scaling factor.

Ø In Full scaling, power supply voltage & all terminal voltages are scaled down proportionally with the device dimensions, but the scaling of voltages may not be very practical in many cases.

Ø In particular, the peripheral and interface circuitry may require certain voltage levels for all inputs and output voltages, which in turn would necessitate multiple power supply voltages & complicated level – shifter arrangements.

Ø Hence for these reasons, constant voltage scaling is usually preferred over full scaling.

2. Constant voltage scaling:

v In Constant voltage scaling, all dimensions of the MOSFET are reduced by a factor of ‘s’, but power supply & terminal voltage remain unchanged.

v In Constant voltage scaling, drain current density and power density are increased which may eventually cause serious reliability problem for the scaled transistor such as electro-migration, hot carrier degradation, oxide breakdown & electrical overstress.