Computer system assigns the binary addresses to the memory locations. However, The system uses amount of bits to address a memory location.

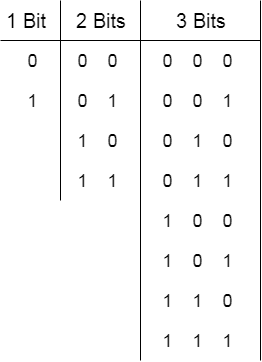

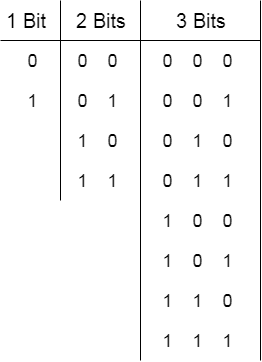

Using 1 bit, we can address two memory locations. Using 2 bits we can address 4 and using 3 bits we can address 8 memory locations.

A pattern can be identified in the mapping between the number of bits in the address and the range of the memory locations.

We know,

1. Using 1 Bit we can represent 2^1 i.e 2 memory locations.

2. Using 2 bits, we can represent 2^2 i.e. 4 memory locations.

3. Using 3 bits, we can represent 2^3 i.e. 8 memory locations.

4. Therefore, if we generalize this,

5. Using n bits, we can assign 2^n memory locations.

6.

7. n bits of address → 2 ^ n memory locations

these n bits can be divided into two parts, that are, K bits and (n-k) bits.

Physical address space in a system can be defined as the size of the main memory. It is really important to compare the process size with the physical address space. The process size must be less than the physical address space.

Physical Address Space = Size of the Main Memory

If, physical address space = 64 KB = 2 ^ 6 KB = 2 ^ 6 X 2 ^ 10 Bytes = 2 ^ 16 bytes

Let us consider,

word size = 8 Bytes = 2 ^ 3 Bytes

Hence,

Physical address space (in words) = (2 ^ 16) / (2 ^ 3) = 2 ^ 13 Words

Therefore,

Physical Address = 13 bits

In General,

If, Physical Address Space = N Words

then, Physical Address = log2 N

Logical address space can be defined as the size of the process. The size of the process should be less enough so that it can reside in the main memory.

Let's say,

Logical Address Space = 128 MB = (2 ^ 7 X 2 ^ 20) Bytes = 2 ^ 27 Bytes

Word size = 4 Bytes = 2 ^ 2 Bytes

Logical Address Space (in words) = (2 ^ 27) / (2 ^ 2) = 2 ^ 25 Words

Logical Address = 25 Bits

In general,

If, logical address space = L words

Then, Logical Address = Log2L bits

The Word is the smallest unit of the memory. It is the collection of bytes. Every operating system defines different word sizes after analyzing the n-bit address that is inputted to the decoder and the 2 ^ n memory locations that are produced from the decoder.

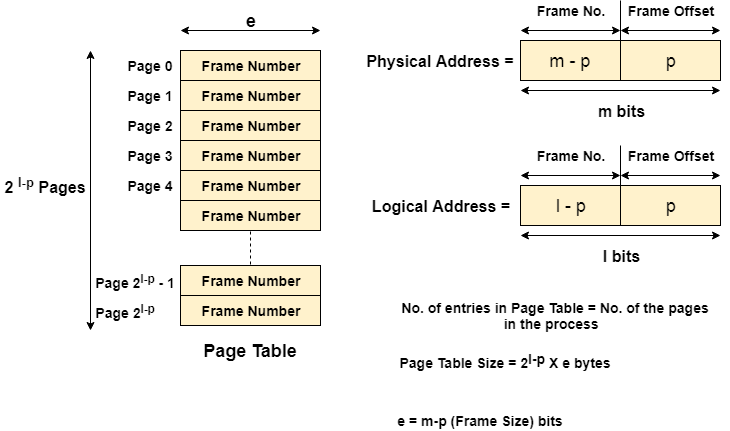

Page Table

Page Table is a data structure used by the virtual memory system to store the mapping between logical addresses and physical addresses.

Logical addresses are generated by the CPU for the pages of the processes therefore they are generally used by the processes.

Physical addresses are the actual frame address of the memory. They are generally used by the hardware or more specifically by RAM subsystems.

The image given below considers,

Physical Address Space = M words

Logical Address Space = L words

Page Size = P words

Physical Address = log 2 M = m bits

Logical Address = log 2 L = l bits

page offset = log 2 P = p bits

The CPU always accesses the processes through their logical addresses. However, the main memory recognizes physical address only.

In this situation, a unit named as Memory Management Unit comes into the picture. It converts the page number of the logical address to the frame number of the physical address. The offset remains same in both the addresses.

To perform this task, Memory Management unit needs a special kind of mapping which is done by page table. The page table stores all the Frame numbers corresponding to the page numbers of the page table.

In other words, the page table maps the page number to its actual location (frame number) in the memory.

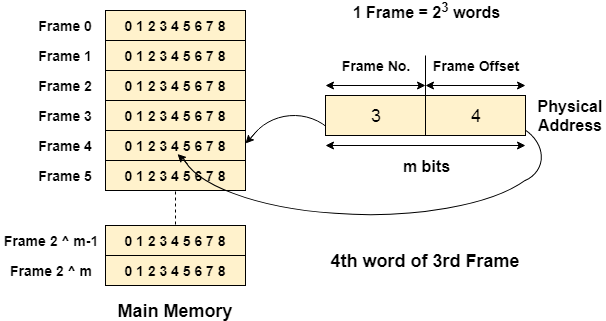

In the image given below shows, how the required word of the frame is accessed with the help of offset.