FET biasing

Unlike BJTs, thermal runaway does not occur with FETs, as already discussed in our blog. However, the wide differences in maximum and minimum transfer characteristics make IDlevels unpredictable with simple fixed-gate bias voltage. To obtain reasonable limits on quiescent drain currents ID and drain-source voltage VDS, source resistor and potential divider bias techniques must be used. With few exceptions, MOSFET bias circuits are similar to those used for JFETs. Various FET biasing circuits are discussed below:

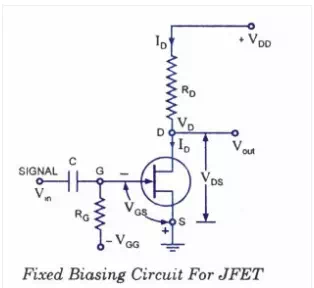

Fixed Bias.

DC bias of a FET device needs setting of gate-source voltage VGS to give desired drain current ID . For a JFET drain current is limited by the saturation current IDS. Since the FET has such a high input impedance that no gate current flows and the dc voltage of the gate set by a voltage divider or a fixed battery voltage is not affected or loaded by the FET. Fixed dc bias is obtained using a battery VQG. This battery ensures that the gate is always negative with respect to source and no current flows through resistor RG and gate terminal that is IG =0. The battery provides a voltage VGS to bias the N-channel JFET, but no resulting current is drawn from the battery VGG. Resistor RG is included to allow any ac signal applied through capacitor C to develop across RG. While any ac signal will develop across RG, the dc voltage drop across RG is equal to IG RG i.e. 0 volt.

The gate-source voltage VGS is then

VGS = – vG – vs = – vGG – 0 = – VGG

The drain -source current ID is then fixed by the gate-source voltage as determined by equation.

This current then causes a voltage drop across the drain resistor RD and is given as VRD = ID RD and output voltage, Vout = VDD – ID RD

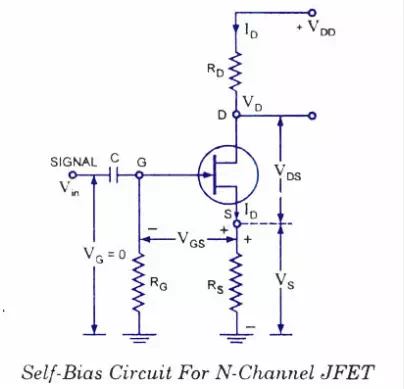

Self-Bias.

This is the most common method for biasing a JFET. Self-bias circuit for N-channel JFET is shown in figure.

Since no gate current flows through the reverse-biased gate-source, the gate current IG = 0 and, therefore,vG = iG RG = 0

With a drain current

ID the voltage at the S is

Vs= ID Rs

The gate-source voltage is then

VGs = VG – Vs = 0 – ID Rs = – ID Rs

So voltage drop across resistance Rs provides the biasing voltage VGg and no external source is required for biasing and this is the reason that it is called self-biasing.

The operating point (that is zero signal ID and VDS) can easily be determined from equation and equation given below :

VDS = VDD – ID (RD + RS)

Thus dc conditions of JFET amplifier are fully specified. Self biasing of a JFET stabilizes its quiescent operating point against any change in its parameters like transconductance. Let the given JFET be replaced by another JFET having the double conductance then drain current will also try to be double but since any increase in voltage drop across Rs, therefore, gate-source voltage, VGS becomes more negative and thus increase in drain current is reduced.

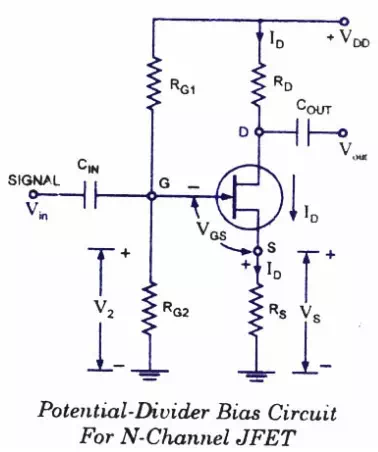

Potential-Divider Biasing.

A slightly modified form of dc bias is provided by the circuit shown in figure. The resistors RGl and RG2 form a potential divider across drain supply VDD. The voltage V2 across RG2provides the necessary bias. The additional gate resistor RGl from gate to supply voltage facilitates in larger adjustment of the dc bias point and permits use of larger valued RS.

The gate is reverse biased so that IG = 0 and gate voltage

VG =V2 = (VDD/R G1 + R G2 ) *RG2

And

VGS = vG – vs = VG – ID Rs

The circuit is so designed that ID Rs is greater than VG so that VGS is negative. This provides correct bias voltage.

The operating point can be determined as ID = (V2 – VGS)/ RS And VDS = VDD – ID (RD + RS)