Asynchronous Sequential Circuits

Let us recall what a counter is. A counter is nothing but a sequential circuit that experiences a specific sequence of states when certain input pulses are applied to the circuit. The input pulses, also known as count pulses, can be pulses from a clock or an external source, which can occur at random or at specific intervals of time. The sequence of states in a counter can conform to a binary or any other sequence.

A counter can be of two types:

Let us explore asynchronous sequential circuits, which consists of flip-flops. A flip-flop is a basic memory element that can store one bit of information. Asynchronous sequential circuits change their states and output values whenever there is a change in input values.

In asynchronous sequential circuits, the inputs are levels and there are no clock pulses. The input events drive the circuit. In other words, the circuit is said to be asynchronous if it is not driven by a periodic clock signal to synchronize its internal states.

For example, consider a ripple counter, which is asynchronous. In the ripple counter:

To be more specific, a flip-flop is a memory device controlled by a clock. It means a flip-flop stores the input value and sends the stored value as output only when there is a clock signal.

If we connect many flip-flops together, they can save data. This data can be the value of a numeric character in a computer storage or any other piece of information.

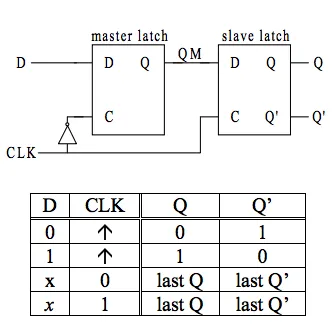

The following figure represents a D flip-flop, a popular type of flip-flop, and its truth table:

|

The following figure is the timing diagram for the preceding flip-flop:

|

In this example, the flip-flop evaluates its D input and changes its Q and Q' outputs only at the rising edge of a controlling clock (CLK) signal.

You can observe that the slave latch is open as long as CLK=1. It changes its state only at the beginning of this interval. Its state does not change during the rest of the interval.

Therefore, the master and slave latches are not open at the same time. The entire flip-flop is never transparent, meaning the output of the flip-flop changes only on a single type (positive or negative) of the clock edge.