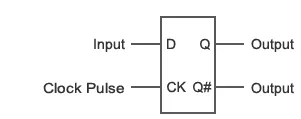

Clocked D Flip-Flop

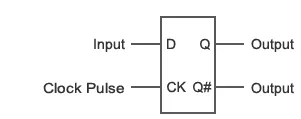

The D flip-flop captures the value of the D input at the time of the rising edge (L→H) and/or falling edge (H→L) of the incoming clock pulse (CK), and outputs this value from the Q output.

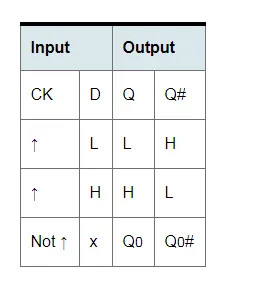

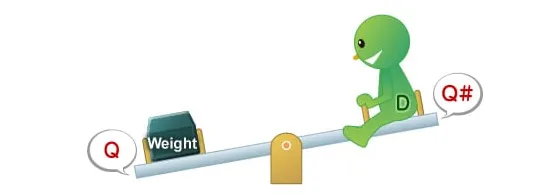

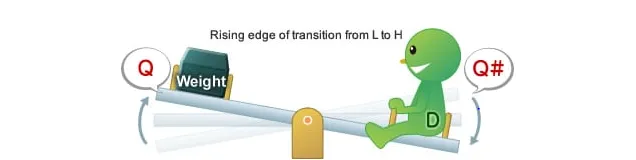

Let’s reuse the seesaw analogy to explain the D flip-flop. Figure 8 shows an initial state. Input D goes to H when Mr. D gets on the seesaw; it goes to L when Mr. D gets off. A weight that is lighter than Mr. D rests on the other side of the seesaw. And unlike a real seesaw, the seesaw we are imagining can change its state only at the moment when it is receiving the rising edge of the clock pulse.

Now that Mr. D’s side is down, it must stay down at least until the next time that the CK signal changes from L to H. In other words, the seesaw " remembers" its state at least until CK completes both its current H cycle and subsequent L cycle, regardless of how many times Mr. D jumps off and gets back on in the meantime.

The D flip-flop, in other words, is a clock-synchronized sequential logic circuit that remembers the state in effect during the instant that the CK signal last changed from L to H.

D flip-flops are a basic building block of sequential circuitry, and have a wide range of uses. They can be configured together in multiple stages to implement shift registers and clock division circuits. They are also found in internal CPU registers.